|

|

PDF S1D15206 Data sheet ( Hoja de datos )

| Número de pieza | S1D15206 | |

| Descripción | LCD Driver | |

| Fabricantes | Epson | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de S1D15206 (archivo pdf) en la parte inferior de esta página. Total 30 Páginas | ||

|

No Preview Available !

4. S1D15206 Series

Rev. 3.5

1 page

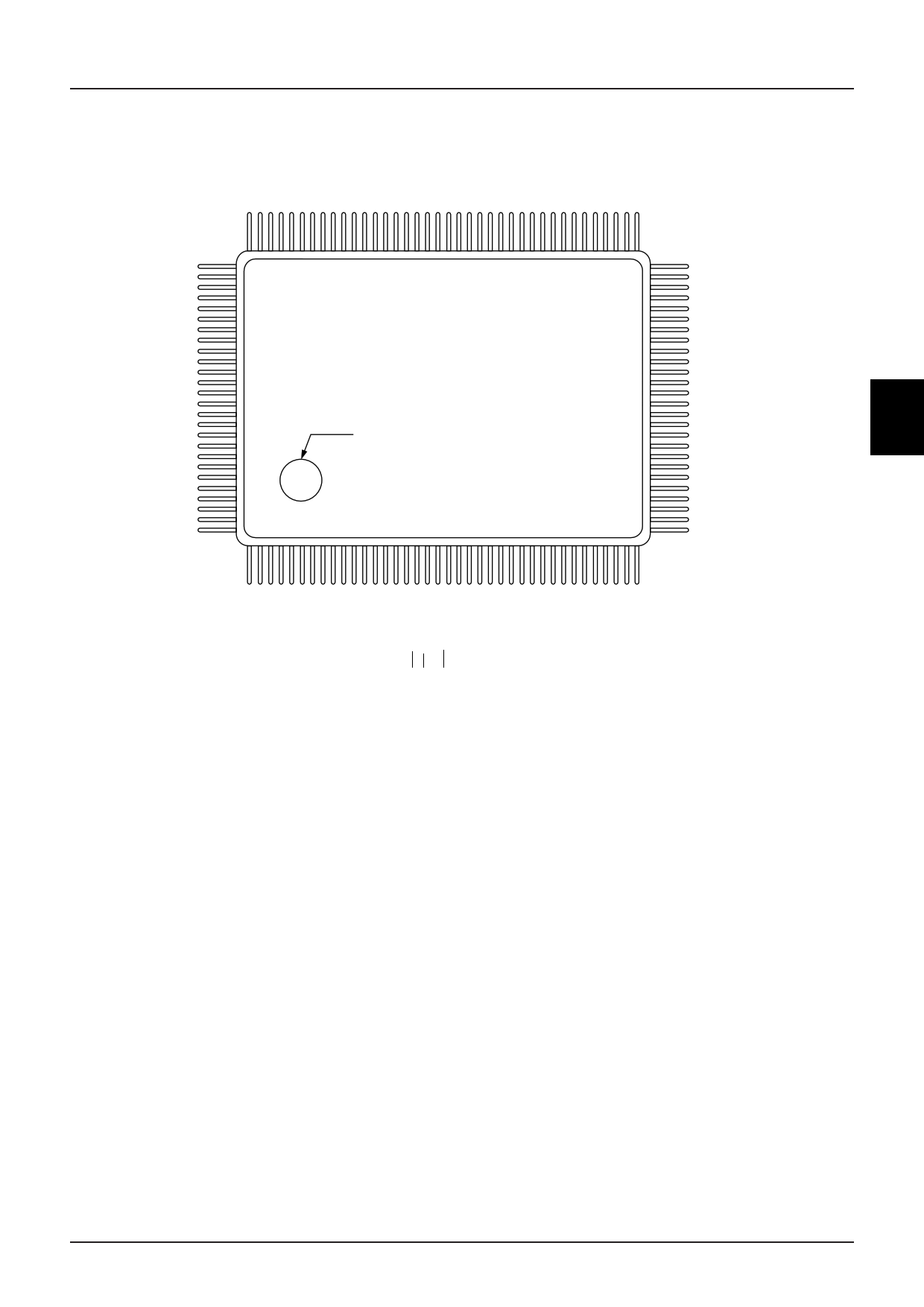

4. PIN LAYOUT

Package Pin Assignment

SEG54

SEG55

SEG56

SEG57

SEG58

SEG59

SEG60

SEG61

SEG62

SEG63

SEG64

SEG65

SEG66

SEG67

SEG68

SEG69

SEG70

SEG71

SEG72

SEG73

SEG74

SEG75

SEG76

SEG77

SEG78

SEG79

(COM15)

(COM14)

(COM13)

(COM12)

(COM11)

(COM10)

(COM 9)

(COM 8)

(COM 7)

(COM 6)

(COM 5)

(COM 4)

(COM 3)

(COM 2)

(COM 1)

(COM 0)

103

110

120

128

Index

S1D15206 Series

SEG15

64 SEG14

SEG13

SEG12

SEG11

SEG10

SEG9

SEG8

SEG7

SEG6

SEG5

SEG4

SEG3

SEG2

50 SEG1

SEG0

COMS

[COM15]

COM15 (COM31) [COM14]

COM14 (COM30) [COM13]

COM13 (COM29) [COM12]

COM12 (COM28) [COM11]

COM11 (COM27) [COM10]

COM10 (COM26) [COM 9]

COM9 (COM25) [COM 8]

39 COM8 (COM24) [COM 7]

COM7 (COM23) [COM 6]

* Pin name in ( ) apply to S1D15208.

* Pin name in [ ] apply to S1D15206D10**(CMOS Pin=Type B).

Rev.3.5

EPSON

4–3

5 Page

S1D15206 Series

CS1

CS2

D7(S1)

D7 D6 D5 D4 D3 D2 D1 D0 D7 D6 D5

D6(SCL)

A0

1 2 3 4 5 6 7 8 9 10 11 12

Figure 1

Chip Select Inputs

The S1D15206 series can interface to microprocessor when CS1 is

LOW and CS2 is HIGH.

When these pins are set to any other combination, D0 to D7 are high

impedance. A0, RD, and WR input are disabled. However, the reset

signal is entered regardless of CS1 and CS2 setup. The internal IC

status including LCD driver circuit is held until a reset signal is

entered.

Access to Display Data RAM and Internal Registers

The S1D15206 series can perform a series of pipeline processing

between LSI’s using bus holder of internal data bus in order to match

the operating frequency of display RAM and internal registers with

the microprocessor. For example, the microprocessor reads data

from display RAM in the first read (dummy) cycle, stores it in bus

holder, and outputs it onto system bus in the next data read cycle.

Also, the microprocessor temporarily stores display data in bus

holder, and stores it in display RAM until the next data write cycle

starts.

When viewed from the microprocessor, the S1D15206 series access

speed greatly depends on the cycle time rather than access time to the

display RAM (tACC and tDS). It shows the data transfer speed to/

from the microprocessor can increase. If the cycle time is inappro-

priate, the microprocessor can insert the NOP instruction that is

equivalent to the wait cycle setup. However, there is a restriction in

the display RAM read sequence. When an address is set, the

specified address data is NOT output at the immediately following

read instruction. The address data is output during second data read.

A single dummy read must be inserted after address setup and after

write cycle (refer to Figure 2).

•Write

MPU

WR

DATA

Internal

timing

Bus holder

Write signal

n

Latched

n

n+1

n+1

n+2

n+2

n+3

n+3

•Read

MPU

WR

RD

DATA

Internal

timing

Address

preset

Read signal

Column

address

Bus holder

Rev.3.5

NN

n n+1

Preset

N

Incremented

N+1

N+2

N

Set address n

n n+1 n+2

Dummy read

Figure 2

EPSON

Read address n

Read address n+1

n: Current data

N: Dummy data

4–9

11 Page | ||

| Páginas | Total 30 Páginas | |

| PDF Descargar | [ Datasheet S1D15206.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| S1D15206 | LCD Driver | Epson |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |