|

|

PDF WV3HG128M72AER-D6 Data sheet ( Hoja de datos )

| Número de pieza | WV3HG128M72AER-D6 | |

| Descripción | 1GB - 128Mx72 DDR2 SDRAM REGISTERED | |

| Fabricantes | White Electronic Designs | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de WV3HG128M72AER-D6 (archivo pdf) en la parte inferior de esta página. Total 10 Páginas | ||

|

No Preview Available !

White Electronic Designs WV3HG128M72AER-D6

ADVANCED*

1GB – 128Mx72 DDR2 SDRAM REGISTERED, w/PLL

FEATURES

240-pin, dual in-line memory module

Fast data transfer rates: PC2-6400*, PC2-5300*,

PC2-4300 and PC2-3200

Utilizes 800, 667, 533 and 400 MT/s DDR2 SDRAM

components

VCC = VCCQ = 1.8V

JEDEC standard 1.8V I/O (SSTL_18-compatible)

Differential data strobe (DQS, DQS#) option

Four-bit prefetch architecture

DLL to align DQ and DQS transitions with CK

Multiple internal device banks for concurrent

operation

Supports duplicate output strobe (RDQS/RDQS#)

Programmable CAS# latency (CL): 3, 4, 5 and 6

Adjustable data-output drive strength

On-die termination (ODT)

Posted CAS# latency: 0, 1, 2, 3 and 4

Serial Presence Detect (SPD) with EEPROM

64ms: 8,192 cycle refresh

Gold edge contacts

wwwP.DraotdauSchteiest4leUa.cdo-mfree

RoHS compliant

Package option

• 240 Pin DIMM

• PCB – 29.97mm (1.18") Max

DESCRIPTION

The WV3HG128M72AER is a 128Mx72 Double Data Rate

DDR2 SDRAM high density module. This memory module

consists of eighteen 128Mx4 bit with 4 banks DDR2

Synchronous DRAMs in FBGA packages, mounted on a

240-pin DIMM FR4 substrate.

* This product is under development, is not qualified or characterized and is subject to

change or cancellation without notice.

NOTE: Consult factory for availability of:

• Vendor source control options

• Industrial temperature option

Clock Speed

CL-tRCD-tRP

* Consult factory for availability

PC2-3200

200MHz

3-3-3

OPERATING FREQUENCIES

PC2-4300

266MHz

4-4-4

PC2-5300*

333MHz

5-5-5

PC2-6400*

400MHz

6-6-6

March 2005

Rev. 0

1 White Electronic Designs Corporation • (602) 437-1520 • www.wedc.com

1 page

White Electronic Designs WV3HG128M72AER-D6

ADVANCED

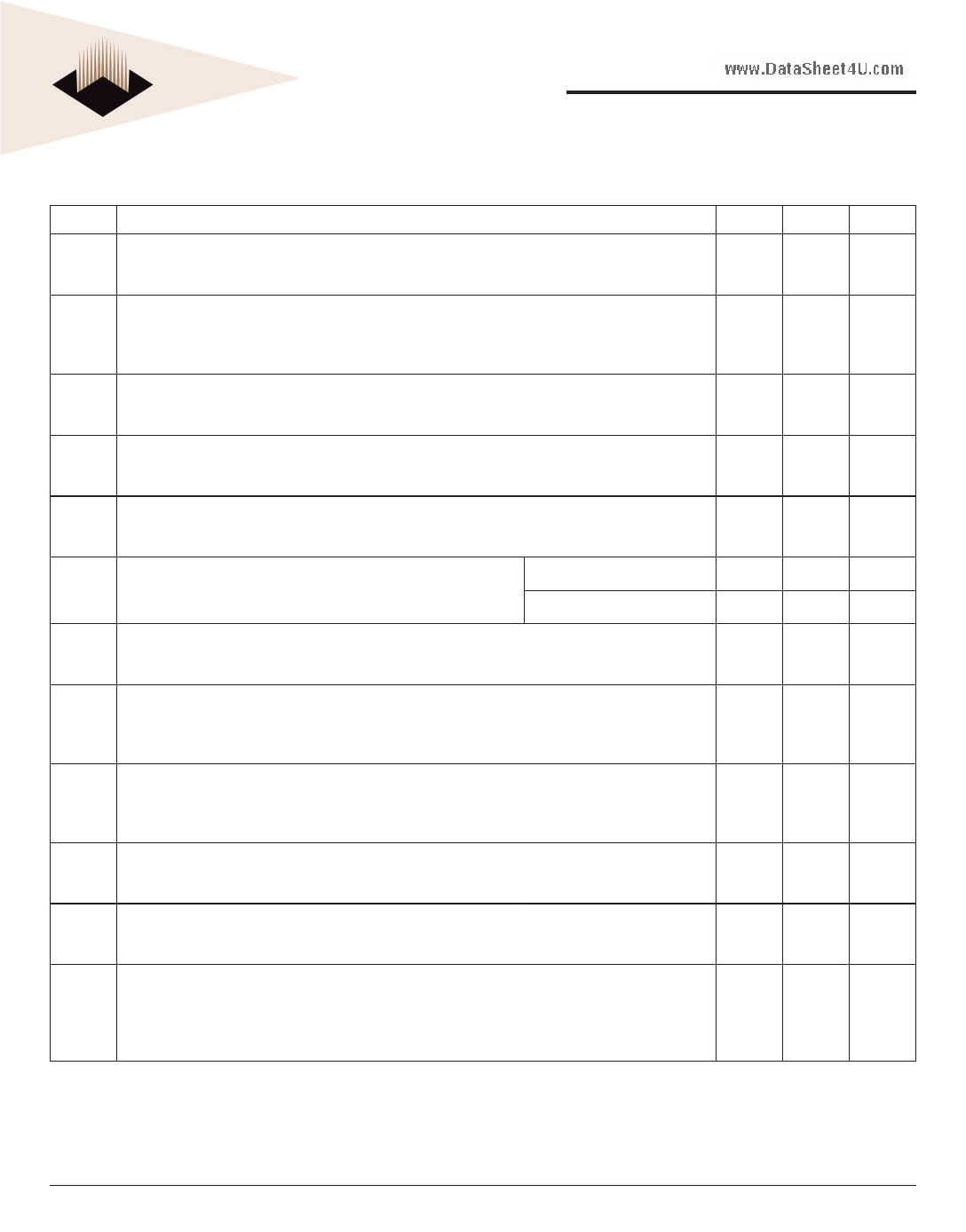

DDR2 IDD SPECIFICATIONS AND CONDITIONS

Includes DDR2 SDRAM components only

Symbol

IDD0

IDD1

IDD2P

IDD2Q

IDD2N

IDD3P

Proposed Conditions

Operating one bank active-precharge current;

tCK = tCK(IDD), tRC = tRC(IDD), tRAS = tRASmin(IDD); CKE is HIGH, CS\ is HIGH between valid commands;

Address bus inputs are SWITCHING; Data bus inputs are SWITCHING

Operating one bank active-read-precharge current;

IOUT = 0mA; BL = 4, CL = CL(IDD), AL = 0; tCK = tCK(IDD), tRC = tRC (IDD), tRAS = tRASmin(IDD), tRCD = tRCD(IDD);

CKE is HIGH, CS\ is HIGH between valid commands; Address businputs are SWITCHING; Data pattern is

same as IDD6W

Precharge power-down current;

All banks idle; tCK = tCK(IDD); CKE is LOW; Other control and address bus inputs are STABLE; Data bus

inputs are FLOATING

Precharge quiet standby current;

All banks idle; tCK = tCK(IDD); CKE is HIGH, CS\ is HIGH; Other control and address bus inputsare STABLE;

Data bus inputs are FLOATING

Precharge standby current;

All banks idle; tCK = tCK(IDD); CKE is HIGH, CS\ is HIGH; Other control and address bus inputs are

SWITCHING; Data bus inputs are SWITCHING

Active power-down current;

All banks open; tCK = tCK(IDD); CKE is LOW; Other control and address

bus inputs are STABLE; Data bus inputs are FLOATING

Fast PDN Exit MRS(12) = 0mA

Slow PDN Exit MRS(12) = 1mA

IDD3N Active standby current;

All banks open; tCK = tCK(IDD), tRAS = tRASmax(IDD), tRP = tRP(IDD); CKE is HIGH, CS\ is HIGH between valid

commands; Other control and address bus inputs are SWITCHING; Data bus inputs are SWITCHING

IDD6W

Operating burst write current;

All banks open, Continuous burst writes; BL = 4, CL = CL(IDD), AL = 0; tCK = tCK(IDD), tRAS = tRASmax(IDD), tRP

= tRP(IDD); CKE is HIGH, CS\ is HIGH between valid commands; Address bus inputs are SWITCHING; Data

bus inputs are SWITCHING

wwIDwD.6DR ataSOhpeereatt4inUg .bcuorsmt read current;

All banks open, Continuous burst reads, IOUT = 0mA; BL = 4, CL = CL(IDD), AL = 0; tCK = tCK(IDD), tRAS =

tRASmax(IDD), tRP = tRP(IDD); CKE is HIGH, CS\ is HIGH between valid commands; Address bus inputs are

SWITCHING; Data pattern is same as IDD6W

IDD5B Burst auto refresh current;

tCK = tCK(IDD); Refresh command at every tRFC(IDD) interval; CKE is HIGH, CS\ is HIGH between valid

commands; Other control and address bus inputs are SWITCHING; Data bus inputs are SWITCHING

IDD6 Self refresh current;

CK and CK\ at 0V; CKE 0.2V; Other control and address bus inputs

are FLOATING; Data bus inputs are FLOATING

IDD7 Operating bank interleave read current;

All bank interleaving reads, IOUT = 0mA; BL = 4, CL = CL(IDD), AL = tRCD(IDD)-1*tCK(IDD); tCK = tCK(IDD), tRC =

tRC(IDD), tRRD = tRRD(IDD), tRCD = 1*tCK(IDD); CKE is HIGH, CS\ is HIGH between valid commands; Address

bus inputs are STABLE during DESELECTs; Data pattern is same as IDD6R; Refer to the following page for

detailed timing conditions

534

2,420

2,640

730

1,110

1,090

1,190

600

1,840

3,550

3,230

3,610

740

5,540

403

2,250

2,400

670

1,110

1,060

1,130

570

1,730

2,810

2,730

3,430

680

5,210

Units

mA

mA

mA

mA

mA

mA

mA

mA

mA

mA

mA

mA

mA

March 2005

Rev. 0

5 White Electronic Designs Corporation • (602) 437-1520 • www.wedc.com

5 Page | ||

| Páginas | Total 10 Páginas | |

| PDF Descargar | [ Datasheet WV3HG128M72AER-D6.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| WV3HG128M72AER-D6 | 1GB - 128Mx72 DDR2 SDRAM REGISTERED | White Electronic Designs |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |