|

|

PDF 74HC373 Data sheet ( Hoja de datos )

| Número de pieza | 74HC373 | |

| Descripción | Octal D-type transparent latch | |

| Fabricantes | NXP Semiconductors | |

| Logotipo | ||

Hay una vista previa y un enlace de descarga de 74HC373 (archivo pdf) en la parte inferior de esta página. Total 25 Páginas | ||

|

No Preview Available !

74HC373; 74HCT373

Octal D-type transparent latch; 3-state

Rev. 6 — 26 February 2016

Product data sheet

1. General description

The 74HC373; 74HCT373 is an octal D-type transparent latch with 3-state outputs. The

device features latch enable (LE) and output enable (OE) inputs. When LE is HIGH, data

at the inputs enter the latches. In this condition the latches are transparent, a latch output

will change each time its corresponding D-input changes. When LE is LOW the latches

store the information that was present at the inputs a set-up time preceding the

HIGH-to-LOW transition of LE. A HIGH on OE causes the outputs to assume a

high-impedance OFF-state. Operation of the OE input does not affect the state of the

latches. Inputs include clamp diodes. This enables the use of current limiting resistors to

interface inputs to voltages in excess of VCC.

2. Features and benefits

Input levels:

For 74HC373: CMOS level

For 74HCT373: TTL level

3-state non-inverting outputs for bus oriented applications

Common 3-state output enable input

Functionally identical to the 74HC563; 74HCT563 and 74HC573; 74HCT573

Complies with JEDEC standard no. 7 A

ESD protection:

HBM JESD22-A114F exceeds 2000 V

MM JESD22-A115-A exceeds 200 V

Multiple package options

Specified from 40 C to +85 C and from 40 C to +125 C

3. Ordering information

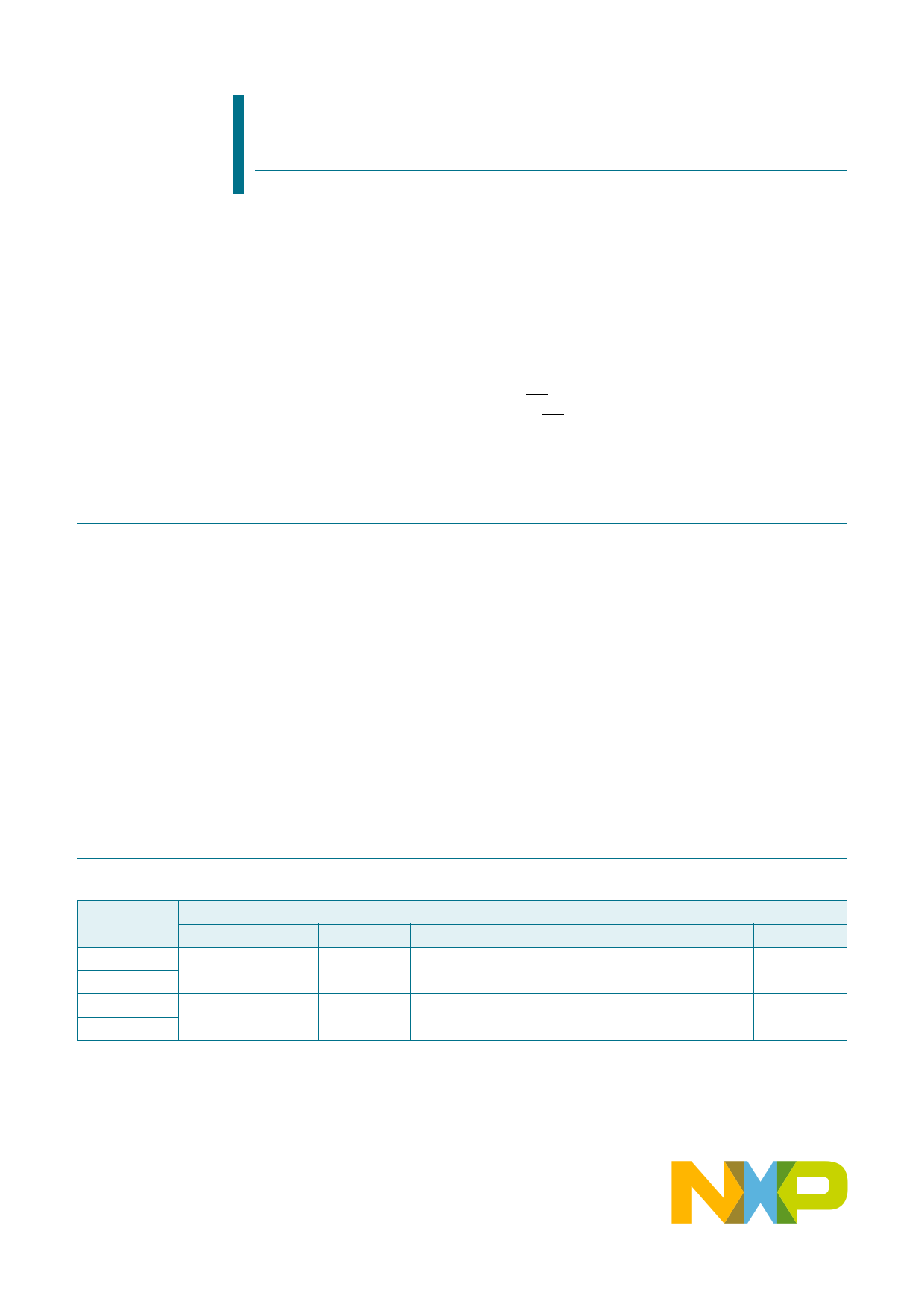

Table 1. Ordering information

Type number Package

Temperature range Name

74HC373D 40 C to +125 C SO20

74HCT373D

74HC373DB 40 C to +125 C SSOP20

74HCT373DB

Description

plastic small outline package; 20 leads;

body width 7.5 mm

plastic shrink small outline package; 20 leads;

body width 5.3 mm

Version

SOT163-1

SOT339-1

1 page

NXP Semiconductors

74HC373; 74HCT373

Octal D-type transparent latch; 3-state

6. Functional description

6.1 Function table

Table 3. Function table[1]

Operating mode

Control

OE

Enable and read register

(transparent mode)

L

Latch and read register

L

Latch register and disable H

outputs

LE

H

L

X

Input

Dn

L

H

l

h

X

[1] H = HIGH voltage level;

h = HIGH voltage level one set-up time prior to the HIGH-to-LOW LE transition;

L = LOW voltage level;

I = LOW voltage level one set-up time prior to the HIGH-to-LOW LE transition;

X = don’t care;

Z = high-impedance OFF-state.

7. Limiting values

Internal latches

L

H

L

H

X

Output

Qn

L

H

L

H

Z

Table 4. Limiting values

In accordance with the Absolute Maximum Rating System (IEC 60134). Voltages are referenced to GND (ground = 0 V).

Symbol

Parameter

Conditions

Min Max Unit

VCC

IIK

IOK

IO

ICC

IGND

Tstg

Ptot

supply voltage

input clamping current

output clamping current

output current

supply current

ground current

storage temperature

total power dissipation

VI < 0.5 V or VI > VCC + 0.5 V

VO < 0.5 V or VO > VCC + 0.5 V

VO = 0.5 V to (VCC + 0.5 V)

SO20 package

SSOP20 package

0.5

-

-

-

-

-

65

[1] -

[2] -

+7

20

20

35

+70

70

+150

500

500

V

mA

mA

mA

mA

mA

C

mW

mW

TSSOP20 package

[2] -

500 mW

DHVQFN20 package

[3] -

500 mW

[1] For SO20: Ptot derates linearly with 8 mW/K above 70 C.

[2] For SSOP20 and TSSOP20 packages: Ptot derates linearly with 5.5 mW/K above 60 C.

[3] For DHVQFN20 package: Ptot derates linearly with 4.5 mW/K above 60 C.

74HC_HCT373

Product data sheet

All information provided in this document is subject to legal disclaimers.

Rev. 6 — 26 February 2016

© NXP Semiconductors N.V. 2016. All rights reserved.

5 of 25

5 Page

NXP Semiconductors

74HC373; 74HCT373

Octal D-type transparent latch; 3-state

Table 8. Dynamic characteristics 74HC373 …continued

Voltages are referenced to GND (ground = 0 V); CL = 50 pF unless otherwise specified; for test circuit see Figure 12.

Symbol Parameter

Conditions

Min Typ Max Unit

Tamb = 40 C to +85 C

tpd propagation delay

Dn to Qn; see Figure 8

VCC = 2.0 V

VCC = 4.5 V

VCC = 6.0 V

LE to Qn; see Figure 9

[1]

-

-

-

- 190 ns

- 38 ns

- 33 ns

ten enable time

tdis disable time

tt transition time

tW pulse width

tsu set-up time

th hold time

VCC = 2.0 V

VCC = 4.5 V

VCC = 6.0 V

OE to Qn; see Figure 10

VCC = 2.0 V

VCC = 4.5 V

VCC = 6.0 V

OE to Qn; see Figure 10

VCC = 2.0 V

VCC = 4.5 V

VCC = 6.0 V

Qn; see Figure 8 and Figure 9

VCC = 2.0 V

VCC = 4.5 V

VCC = 6.0 V

LE HIGH; see Figure 9

VCC = 2.0 V

VCC = 4.5 V

VCC = 6.0 V

Dn to LE; see Figure 11

VCC = 2.0 V

VCC = 4.5 V

VCC = 6.0 V

Dn to LE; see Figure 11

VCC = 2.0 V

VCC = 4.5 V

VCC = 6.0 V

-

-

-

[2]

-

-

-

[3]

-

-

-

[4]

-

-

-

- 220 ns

- 44 ns

- 37 ns

- 190 ns

- 38 ns

- 33 ns

- 190 ns

- 38 ns

- 33 ns

- 75 ns

- 15 ns

- 13 ns

100 -

20 -

17 -

- ns

- ns

- ns

65 -

13 -

11 -

- ns

- ns

- ns

5 - - ns

5 - - ns

5 - - ns

74HC_HCT373

Product data sheet

All information provided in this document is subject to legal disclaimers.

Rev. 6 — 26 February 2016

© NXP Semiconductors N.V. 2016. All rights reserved.

11 of 25

11 Page | ||

| Páginas | Total 25 Páginas | |

| PDF Descargar | [ Datasheet 74HC373.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| 74HC373 | Octal D-type transparent latch 3-state | Philips |

| 74HC373 | Octal D-type transparent latch | NXP Semiconductors |

| 74HC374 | Octal D-type flip-flop positive edge-trigger 3-state | Philips |

| 74HC374 | Octal 3-State Non-Inverting D Flip-Flop | ON Semiconductor |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |