|

|

PDF LTC6946 Data sheet ( Hoja de datos )

| Número de pieza | LTC6946 | |

| Descripción | Ultralow Noise and Spurious 0.37GHz to 6.39GHz Integer-N Synthesizer | |

| Fabricantes | Linear Technology | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de LTC6946 (archivo pdf) en la parte inferior de esta página. Total 30 Páginas | ||

|

No Preview Available !

LTC6946

Ultralow Noise and Spurious

0.37GHz to 6.39GHz Integer-N

Synthesizer with Integrated VCO

Features

Description

nn Low Noise Integer-N PLL with Integrated VCO

nn –226dBc/Hz Normalized In-Band Phase Noise Floor

nn –274dBc/Hz Normalized In-Band 1/f Noise

nn –157dBc/Hz Wideband Output Phase Noise Floor

nn Excellent Spurious Performance

nn Output Divider (1 to 6, 50% Duty Cycle)

nn Output Buffer Muting

nn Low Noise Reference Buffer

nn Charge Pump Current Adjustable from 250µA to

11.2mA

nn Configurable Status Output

nn SPI Compatible Serial Port Control

nn PLLWizard™ Software Design Tool Support

Applications

nn Wireless Base Stations (LTE, WiMAX, W-CDMA, PCS)

nn Broadband Wireless Access

nn Military and Secure Radio

nn Test and Measurement

L, LT, LTC, LTM, Linear Technology and the Linear logo are registered trademarks and

PLLWizard is a trademark of Linear Technology Corporation. All other trademarks are the

property of their respective owners.

The LTC®6946 is a high performance, low noise, 6.39GHz

phase-locked loop (PLL) with a fully integrated VCO,

including a reference divider, phase-frequency detector

(PFD) with phase-lock indicator, ultralow noise charge

pump, integer feedback divider, and VCO output divider.

The charge pump contains selectable high and low voltage

clamps useful for VCO monitoring.

The integrated low noise VCO uses no external components.

It is internally calibrated to the correct output frequency

with no external system support.

The part features a buffered, programmable VCO output

divider with a range of 1 through 6, providing a wide

frequency range.

Frequency Coverage Options

LTC6946-1 LTC6946-2 LTC6946-3 LTC6946-4

O DIV=1 2.240 to 3.740 3.080 to 4.910 3.840 to 5.790 4.200 to 6.390

O DIV=2 1.120 to 1.870 1.540 to 2.455 1.920 to 2.895 2.100 to 3.195

0 DIV=3 0.747 to 1.247 1.027 to 1.637 1.280 to 1.930 1.400 to 2.130

O DIV=4 0.560 to 0.935 0.770 to 1.228 0.960 to 1.448 1.050 to 1.598

O DIV=5 0.448 to 0.748 0.616 to 0.982 0.768 to 1.158 0.840 to 1.278

O DIV=6 0.373 to 0.623 0.513 to 0.818 0.640 to 0.965 0.700 to 1.065

Typical Application

5.7GHz Wideband Receiver

4.7nF

5V

15Ω

0.01µF

2.2µF

97.6Ω57nF

0.01µF

3.3V

0.01µF

3.3V

0.01µF

1µF

+ 1µF

10MHz 51.1Ω

GND

VCP+

CP

VREF+

REF+

REF–

LTC6946-3

3.3V

0.1µF

SPI BUS

BB

VRF+

RF+

RF–

GND

MUTE

1µF

0.01µF

3.3V

0.1µF

68nH

3.3V

100pF

68nH

RF INPUT

SIGNAL

100pF

RF

LO IF

TO IF

PROCESSING

50Ω

6946 TA01a

UNUSED OUTPUT

IS AVAILABLE

FOR OTHER USE

For more information www.linear.com/LTC6946

LTC6946-3 PLL Phase Noise

–80

–90

–100

–110

–120

–130

–140

RMS NOISE = 0.61°

RMS JITTER = 296fs

–150

fRF = 5.7GHz

fPFD = 10MHz

BW = 85kHz

–160

100 1k 10k

100k

1M

OFFSET FREQUENCY (Hz)

10M 40M

6946 TA01b

6946fb

1

1 page

LTC6946

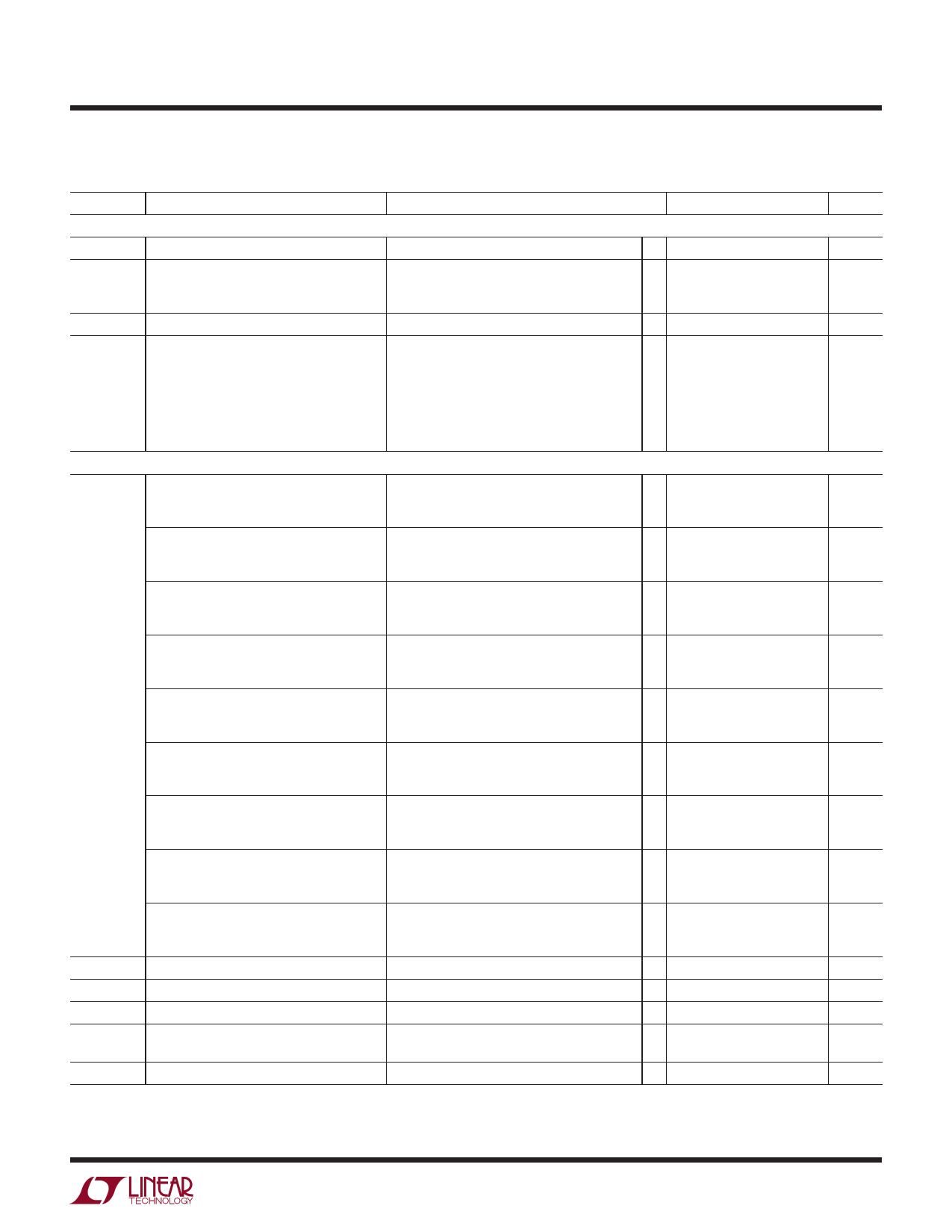

E lectrical Characteristics The l denotes the specifications which apply over the full operating

ojuthnectriwonisteesmppeecriafiteudre(Nraontege2,).oAthlel rvwolitsaegsepseacrieficwaittihonressapreectattoTAGN=D2.5°C. VREF+ = VREF0+ = VD+ = VRF+ = 3.3V, VCP+ = VVCO+ = 5V unless

SYMBOL PARAMETER

CONDITIONS

MIN TYP MAX UNITS

Power Supply Currents

IDD

ICC(5V)

VD+ Supply Current

Sum VCP+, VVCO+ Supply Currents

ICC(REFO)

ICC (3.3V)

VREFO+ Supply Currents

Sum VREF+, VRF+ Supply Currents

Digital Inputs at Supply Levels

IPICCDPPA==L11L1.0=.2m1mAA

REFO Enabled, RZ = ∞

RF Muted, OD[2:0] = 1

RF Enabled, RFO[1:0] =0, OD[2:0] = 1

RF Enabled, RFO[1:0] = 3, OD[2:0] = 1

RF Enabled, RFO[1:0] =3, OD[2:0] = 2

RF Enabled, RFO[1:0] =3, OD[2:0] = 3

RF Enabled, RFO[1:0] =3, OD[2:0] = 4 to 6

PDALL = 1

l

l

l

l

l

l

l

l

l

l

l

l

500

50 63

28 39

405 660

7.8 9.0

65 76

76 86

85 97

103 117

108 123

113 128

195 340

µA

mA

mA

µA

mA

mA

mA

mA

mA

mA

mA

µA

Phase Noise and Spurious

LM

P=h3a.0seGHNzo,isOeD([L2T:C06]9=416-(1N,ofVteCO6)=) 3.0GHz, fRF

10kHz Offset

1MHz Offset

40MHz Offset

–80 dBc/Hz

–130 dBc/Hz

–157 dBc/Hz

Phase Noise (LTC6946-2, fVCO = 4.0GHz, fRF 10kHz Offset

= 4.0GHz, OD[2 :0] = 1 (Note 6))

1MHz Offset

40MHz Offset

–77 dBc/Hz

–127 dBc/Hz

–156 dBc/Hz

Phase Noise (LTC6946-3, fVCO = 5.0GHz, fRF 10kHz Offset

= 5.0GHz, OD[2 :0] = 1 (Note 6))

1MHz Offset

40MHz Offset

–75 dBc/Hz

–126 dBc/Hz

–155 dBc/Hz

VCO Phase Noise (LTC6946-4, fVCO =

10kHz Offset

6.0GHz, fRF = 6.0GHz, OD[2 :0] = 1 (Note 6))

1MHz Offset

40MHz Offset

–73 dBc/Hz

–132 dBc/Hz

–154 dBc/Hz

P=h2a.5se0GNHozis,eO(DL[T2C:609]4=62-3(,NfVoCteO

= 5.0GHz,

6))

fRF

10kHz Offset

1MHz Offset

40MHz Offset

–81 dBc/Hz

–132 dBc/Hz

–155 dBc/Hz

Phase Noise (LTC6946-3, fVCO = 5.0GHz, fRF 10kHz Offset

= 1.667GHz, OD[2 :0] = 3 (Note 6))

1MHz Offset

40MHz Offset

–84 dBc/Hz

–135 dBc/Hz

–156 dBc/Hz

Phase Noise (LTC6946-3, fVCO = 5.0GHz, fRF 10kHz Offset

= 1.25GHz, OD[2 :0] = 4 (Note 6))

1MHz Offset

40MHz Offset

–87 dBc/Hz

–138 dBc/Hz

–156 dBc/Hz

P=h1a.0se0GNHozis,eO(DL[T2C:609]4=65-3(,NfVoCteO

= 5.0GHz,

6))

fRF

10kHz Offset

1MHz Offset

40MHz Offset

–89 dBc/Hz

–140 dBc/Hz

–157 dBc/Hz

Phase Noise (LTC6946-3, fVCO = 5.0GHz, fRF 10kHz Offset

= 0.833GHz, OD[2 :0] = 6 (Note 6))

1MHz Offset

40MHz Offset

–90 dBc/Hz

–141 dBc/Hz

–158 dBc/Hz

LM(NORM) Normalized In-Band Phase Noise Floor

LM(NORM – 1/f) Normalized In-Band 1/f Phase Noise

LM(IB)

In-Band Phase Noise Floor

Integrated Phase Noise from

100Hz to 40MHz

ICP = 11.2mA (Notes 7, 8, 9)

ICP = 11.2mA (Notes 7, 10)

(Notes 7, 8, 9, 11)

(Notes 8, 12)

–226 dBc/Hz

–274 dBc/Hz

–99 dBc/Hz

0.17 °RMS

Spurious

fOFFSET = fPFD, PLL Locked (Notes 8, 12, 13)

–103 dBc

For more information www.linear.com/LTC6946

6946fb

5

5 Page

LTC6946

Pin Functions

VREFO+ (Pin 1): 3.15V to 3.45V Positive Supply Pin for

REFO Circuitry. This pin should be bypassed directly to

the ground plane using a 0.1µF ceramic capacitor as close

to the pin as possible.

REFO (Pin 2): Reference Frequency Output. This produces

a low noise square wave, buffered from the REF± differential

inputs. The output is self-biased and must be AC-coupled

with a 22nF capacitor.

STAT (Pin 3): Status Output. This signal is a configurable

logical OR combination of the UNLOCK, LOCK, ALCHI,

ALCLO, THI and TLO status bits, programmable via the

STATUS register. See the Operation section for more details.

CS (Pin 4): Serial Port Chip Select. This CMOS input initi-

ates a serial port communication burst when driven low,

ending the burst when driven back high. See the Operation

section for more details.

SCLK (Pin 5): Serial Port Clock. This CMOS input clocks

serial port input data on its rising edge. See the Operation

section for more details.

SDI (Pin 6): Serial Port Data Input. The serial port uses

this CMOS input for data. See the Operation section for

more details.

SDO (Pin 7): Serial Port Data Output. This CMOS three-

state output presents data from the serial port during a

read communication burst. Optionally attach a resistor

of >200k to GND to prevent a floating output. See the

Operation section for more details.

VD+ (Pin 8): 3.15V to 3.45V Positive Supply Pin for Serial

Port Circuitry. This pin should be bypassed directly to the

ground plane using a 0.1µF ceramic capacitor as close to

the pin as possible.

MUTE (Pin 9): RF Mute. The CMOS active-low input mutes

the RF± differential outputs while maintaining internal bias

levels for quick response to de-assertion.

GND (Pins 10, 17, 21): Negative Power Supply (Ground).

These pins should be tied directly to the ground plane with

multiple vias for each pin.

RF–, RF+ (Pins 11, 12): RF Output Signals. The VCO

output divider is buffered and presented differentially on

these pins. The outputs are open collector, with 136Ω

(typical) pull-up resistors tied to VRF+ to aid impedance

matching. If used single ended, the unused output should

be terminated to 50Ω. See the Applications Information

section for more details on impedance matching.

VRF+ (Pin 13): 3.15V to 3.45V Positive Supply Pin for

RF Circuitry. This pin should be bypassed directly to the

ground plane using a 0.01µF ceramic capacitor as close

to the pin as possible.

BB (Pin 14): RF Reference Bypass. This output must be

bypassed with a 1.0µF ceramic capacitor to GND. Do not

couple this pin to any other signal.

TUNE (Pin 15): VCO Tuning Input. This frequency control

pin is normally connected to the external loop filter. See

the Applications Information section for more details.

TB (Pin 16): VCO Bypass. This output must be bypassed

with a 2.2µF ceramic capacitor to GND, and is normally

connected to CMA, CMB and CMC with a short trace. Do

not couple this pin to any other signal.

CMC, CMB, CMA (Pins 18, 19, 20): VCO Bias Inputs. These

inputs are normally connected to TB with a short trace

and bypassed with a 2.2µF ceramic capacitor to GND. Do

not couple these pins to any other signal. For best phase

noise performance, do not place a trace between these

pads underneath the package.

VVCO+ (Pin 22): 4.75V to 5.25V Positive Supply Pin for

VCO Circuitry. This pin should be bypassed directly to the

ground plane using both 0.01µF and 1µF ceramic capaci-

tors as close to the pin as possible.

For more information www.linear.com/LTC6946

6946fb

11

11 Page | ||

| Páginas | Total 30 Páginas | |

| PDF Descargar | [ Datasheet LTC6946.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| LTC694 | Microprocessor Supervisory Circuits | Linear Technology |

| LTC694-3.3 | 3.3V Microprocessor Supervisory Circuits | Linear Technology |

| LTC6943 | Dual Precision Instrumentation Switched Capacitor Building Block | Linear |

| LTC6945 | Ultralow Noise and Spurious 0.35GHz to 6GHz Integer-N Synthesizer | Linear |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |